[13B-05]

# DEVELOPMENT OF COMPACT AND HIGH PERFORMANCE KLYSTRON MODULATOR

Y.kanazawa , E.oshita , K.tanaka and H.nakazato Nissin Electric, Co., Ltd. 47, Umezu-Takase-cho, Ukyo-ku, Kyoto 615-8686, Japan

#### Abstract

Recently, it becomes very important to be compact and to have high performance for pulse klystron modulator used for electron linac, etc. Considering the limitation of installation space for apparatus in buildings, smaller modulator is desirable.

We have developed high-flatness (0.3%), high stability (0.5%) and compact pulse klystron modulator. In this paper, the outline of this modulator is mentioned.

# 小型高性能クライストロン電源の開発

#### 1. はじめに

近年、電子リニアック等の加速器において用いられるパルスクライストロン用の電源(モジュレータ)には、安価であることは無論のこと建屋の寸法制限等により小型かつ高性能であることが求められている。

装置を小型化することにより、モジュレータの主性能である出力パルスの平坦度・安定度が損なわれると、クライストロンから出力されるRFパワーが変動し電子ビームの質を悪くしてしまう。

したがって、クライストロン用モジュレータは装置の小型化とともに高性能を維持することが必要となる。

今回、我々は全幅 1.5 m x 奥行き 0.8 mという 小型でかつ高性能 (パルス平坦度 0.3%、パルス安 定度 0.5%)なクライストロン用パルス電源を開発 した。表 1 に本電源の仕様を示す。

### 2. 装置構成

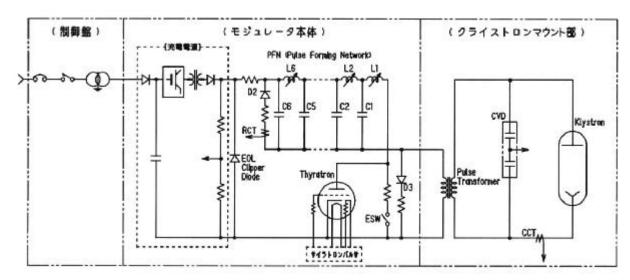

図1に本モジュレータの主回路構成図、図2に外 観写真を示す。

表 1. クライストロン電源仕様

| 出力電圧                 | 1 1 3 k V |

|----------------------|-----------|

| 出力電流                 | 7 5 A     |

| 有効パルス幅*1             | 1.0 µ s   |

| パルス半値幅               | 4.0μs     |

| パルス平坦度               | 1.0%      |

| パルス安定度               | 1.0%      |

| パルス繰返し               | 1 0 p p s |

| パルス立上り <sup>*2</sup> | 1.0 µ s   |

| パルス立下り <sup>*2</sup> | 2.0μs     |

|                      |           |

<sup>\*1)</sup>パルス平坦度を満足する時間

本モジュレータは制御盤、パルス発生部、クライストロン用マウントタンクにより構成される。

パルス発生部内には直流安定化電源、PFN (Pulse Forming Network) クライストロン用 ヒータ電源、パルストランス用バイアス電源等が収納されている。

<sup>\*2)10%~90%</sup>值

図1.クライストロンモジュレータ主回路構成図

図2. 外観写真

クライストロン用マウントタンク内にはクライストロンへ高電圧を供給するためのパルストランス、出力測定用のC分圧器、パルスCT等が収納されている。

### 3. 各部詳細

今回我々は可能な限り装置をコンパクトなもの にし、かつ高性能を維持するために下記の工夫を行った。

# 3.1 PFN回路並列数

PFN回路については、装置を小型化するためには1列が良い事は明らかである。このため、PFNを1列構成として、出力パルスの高平坦度を達成するだけの可変リアクトルの微調整精度を得

ることができるかシミュレーション等を用いて充分に検討を行った。

上記検討の結果、PFN並列数が1列でも充分に 出力パルス平坦度0.3%を達成できることが確認 できたため、PFNは1列構成とした。

#### 3.2 PFNコンデンサ

PFN用コンデンサには下記の理由により、今回は じめて市販のセラミックコンデンサを採用した。

- 1)従来のコンデンサに比べて小型である。

- 2)取付け方向が自由である。

- 3)パルスレーザ等において寿命に関し充分に実 績がある。(10<sup>9</sup>ショット以上)

- 4)内部インダクタンスが極めて小さい。

しかし、セラミックコンデンサをクライストロンモ ジュレータ用に使用するには、

- 1)電圧係数が大きい。(印加電圧に対する静電 容量変化が大きい。)

- 2)温度係数が大きい。(温度変化に対する静電 容量変化が大きい。)

## 等の欠点がある。

これらの欠点はいずれも出力パルスの平坦度・安定 度に悪影響を及ぼすものであるため、負荷の電子ビームの使われ方、クライストロン電源が設置される 環境等を考慮し検討を行った。

- 1)の電圧係数に関しては、電子ビームの加速エネルギーが一定の条件、つまりクライストロンに印加する電圧が一定の場合はコンデンサの静電容量変化は生じないため、波形に影響が出ない。

- 2)の温度係数については、クライストロン電源を設置される場所が空調されており、年間を通じて温度変化が小さいため、波形に及ぼす影響は少ないことが判明した。また、セラミックコンデンサ自身の内部損失も少ないため、充放電による発熱の影響も無視できた。

上記により、今回PFN用コンデンサにセラミックコンデンサを使用することに問題が無いことが判明したため、これを採用した。

# 4. 試験結果

表 2 に今回のクライストロン電源の試験結果を示す。 P F N 用コンデンサにセラミックコンデンサを使用したが出力電圧の平坦度、安定度は従来同様それぞれ 0.3%、0.5%以下の良好な結果を得ることが出来た。

表2.クライストロン電源試験結果

| ペと・ノフィハーロン モ/// ロバロバ  |           |

|-----------------------|-----------|

| 出力電圧                  | 1 1 3 k V |

| 出力電流                  | 7 5 A     |

| 有効パルス幅*1              | 1.1 µ s   |

| パルス半値幅                | 4.0μs     |

| パルス平坦度                | 0.2%      |

| パルス安定度                | 0.3%      |

| パルス繰返し                | 1 0 p p s |

| パルス立上り <sup>*2</sup>  | 1.0 µ s   |

| パルス立下り <sup>* 2</sup> | 1.2μs     |

- \*1)パルス平坦度を満足する時間

- \*2)10%~90%値

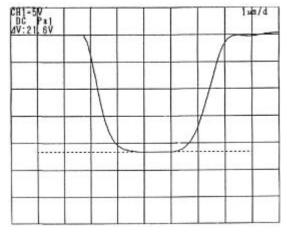

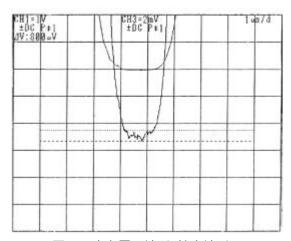

また、定格出力時の電圧波形および拡大波形をそれぞれ図3、図4に示す。

## 5 . おわりに

上記のように今回装置の小型化を図り、PFNコンデンサに初めてセラミックコンデンサを使用したが、従来と同様に出力パルスの平坦度・安定度とも満足の行く結果が得られ、かつコンパクトな電源を製作することが出来た。

図3. 出力電圧波形

図4. 出力電圧波形(拡大波形)