# Zynq 搭載 MTCA. 4 準拠の制御ボード MTCA.4 FPGA(ZYNQ) BOARD

漁師雅次<sup>#,A)</sup>、岩城孝志 <sup>A)</sup>、出口久城 <sup>A)</sup>、林和孝 <sup>A)</sup>、松本利広 <sup>B) C)</sup>、松本隆太郎 <sup>A)</sup>、道園真一郎 <sup>B) C)</sup>

Masatsugu Ryoshi<sup>#,A)</sup>、Takashi Iwaki <sup>A)</sup>、Hisakuni Deguchi <sup>A)</sup>、Kazutaka Hayashi <sup>A)</sup>、Toshihiro Matsumoto <sup>B) C)</sup>、

Ryutaro Matsumoto <sup>A)</sup>、Shinichiro Michizono <sup>B) C)</sup>、

<sup>A)</sup> Mitsubishi Electric TOKKI System Corp.

B) High Energy Accelerator Research Organization (KEK)

<sup>C)</sup> Department of Accelerator Science, Graduate University for Advanced Studies (SOKENDAI)

#### Abstract

We developed a control board that is conforming to the MTCA.4 standard, the FPGA "Zynq" is embedded an ARM Cortex-A9. The Xilinx's "Zynq" SoC (system on chip) is a key device of the new board. Our present control board is adopted as many accelerators, SuperKEKB LLRF, cERL LLRF, and so on, because of it has a user friendly interface (EPICS IOC) in MTCA standard. But the control board does not possess enough extension, because of its size, single width full-size conforming to the MTCA.0 standard, and the size itself is small, so the area we can use for input and output connectors is also small. Moreover, we use Virtex5-FXT (PowerPC440 is embedded), and as advancement of control algorithm, we face difficulties. While, the new board Single-width Full size we made a success of expanding the area double-width Full size. The external interface satisfying many system, has enough space for more expansion by using FMC and  $\mu$  RTM(MTCA Rear Transition Module). Furthermore, by introduce the latest FPGA" Zynq", we bring about improvement of capacity. The new control board is implemented EPICS IOC under an embedded Linux on Cortex-A9. The first application of the new board is STF2 LLRF.

## 1. はじめに

MTCA.0 規格に準拠した現行のディジタル制御ボードは、Single-width Full size であった。様々な用途で利用する際に必要な A/D,D/A,DIO 等の機能拡張性を確保するために、小さな基板面積のベースボードの上に独自の形状のドータカードで 3 段構成とした。リアルタイム処理をする FPGA には、Xilinx 社製の「Virtex5-FXT」を使い、内蔵されている Power PC440 に Linux を組込み、EPICS-IOC とした。リモート制御・モニタのしやすさから、CompactERL、STF、SuperKEKBのディジタル LLRF 制御システム、CompactERL、SuperKEKBのチューナ制御、Super KEKB の軌道フィードバックシステムならびに光伝送システム等、幅広い用途で使われている[1-7]。

しかし、開発してから 5 年経ち、さらなる高速化 と処理能力向上及びユーザビリティの向上のために、 新たな制御ボードを開発した。

## 2. 現行の制御ボードの課題

MTCA.0 の Single-width Full size (73.8\*28.85\*181.5 [mm]) を採用しており、制御システムによく利用される VME や CompactPCI などの 6U サイズ (233.35\*20.1\*169.58 [mm]) のボードに比べて基板面積が狭い。例えばディジタル LLRF 制御ボードの場合、A/D・D/A 各々のドータカードを 3 段目、2 段目として FPGA を実装したベースボードにスタッ

クさせて部品実装面積を確保した。ドータカードに複数チャネルのアナログ信号を入出力するための同軸コネクタを実装するにはパネル面も狭い。そのため、Nicomatic 社製の CMM シリーズの多チャンネル同軸コネクタを採用し、複数チャンネルのアナログ信号の入出力を可能とした<sup>[8]</sup>。しかし、新たに他の機能やインタフェイスが必要になった場合、汎用的な規格のドータカードではなかったため、ハードウェアを新規開発する必要があった。

また、FPGA で行うディジタルフィルタ処理およびフィードバック制御アルゴリズムの高度化に伴い、ロジックゲート・メモリブロック・DSP ブロックなどのリソースに余裕がなくなってきた。その上、フィードバック制御のループディレイを小さくするために、FPGA の処理レイテンシを小さくする必要があった。FPGA の内部のみ 2 倍速のクロック(160MHz)で処理させたが、FPGA 内部の配置配線が難しくなり、少しのロジック変更にも対応が困難になった。

ソフトウェア処理においても FPGA 内部の CPU バスの動作周波数が遅いことが原因で、大容量の DDR2-SDRAM に記録している A/D 変換後のモニタ 信号を Ethernet 経由で外部サーバーへ転送する時間 を短縮できなくなっていた。

## 新しい制御ボードの特長

3.1 新しい制御ボードの概要

現行の制御ボードでは、「拡張性の自由度向上」

<sup>#</sup> ma-ryoshi@west.melos.co.jp

#### **PASJ2014-SUP103**

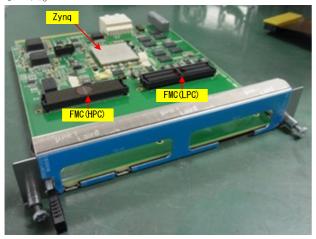

「処理の高度化・高速化」「ソフトウェアの応答性能の向上」などの課題が見えてきた。そこで、現行の制御ボードの課題を解決するために、拡張性と高性能信号処理に対応できる新しい制御ボードを開発した。Figure 1 に新しい制御ボードの外観を示した。拡張性の改善と標準化については、MTCA.4 規格に準拠した Double-width Full size(148.5\*28.85\*181.5 [mm])を採用することで、基板面積およびパネル面積が 2 倍になった。また、外部インタフェイスの機能拡張の標準化ために、独自形状の 3 段重ねドータカードから ANSI/VITA.57.1 で定められているメザニンカードの規格「FMC(FPGA Mezzanine Card)」に変更した。FMCの HPC(High Pin Count)およびLPC(Low Pin Count)それぞれ 1 枚ずつ実装できるようにして、3 段重ねと同等の拡張性を維持した。

ディジタル信号処理の高度化および高速化については、FPGA を Xilinx 社製の最新デバイス「Zynq」に変更した。最新の「Kintex7」と同様のロジックブロック (PL: Programmable Logic) および FPGA に内蔵されている ARM Coatex-A9 (PS: Processing System)と内部 CPU バスが高速で標準的な「AXI-4」が使えるため、より高速で高性能な処理ができるようになった。

Figure 1: MTCA.4 Embedded Linux FPGA card

#### 3.2 MTCA.4 規格の採用

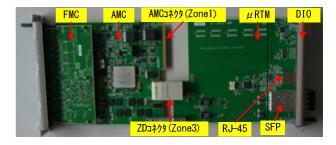

MTCA.4 (Micro TCA Enhancements for Rear I/O and Precision Timing) は PICMG で規格化されている。MTCA.0 を基本に加速器制御および物理学実験のデータ収集装置に必要な高精度タイミング信号が使えるように Zonel「AMC コネクタ」の Port[17..20]が拡張された $^{[9]}$ 。また、シェルフの背面から実装できる $\mu$  RTM (MTCA Rear Transition Module) が使えるため、Figure 2 のように Zone3 の ZD コネクタで信号の入出力を行い、機能を拡張することができる。DESY では RF コンポーネントを実装した $\mu$  RTM を使い、Zone3 を介してアナログ信号のやり取りをしている。ここでは、 $\mu$  RTM で IO の拡張を行っている。Gigabit Ethernet(RJ-45)×1 および SFP×2、DIO×各 8 を追加し、MCH を経由しない外部 Ethernet 通信および高速光通信ができるようにした。

Figure 2: Front board(Left) and  $\mu$  RTM(Right)

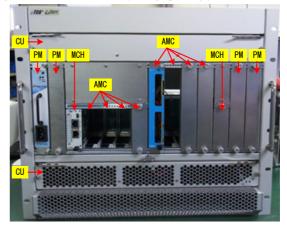

従来の MTCA.0 シェルフに加えて、UBER および TCSJ とともに MTCA.4 対応のシェルフおよびバックプレーンを新たに開発した。Figure 3 は MTCA.4 シェルフの前面、Figure 4 は背面から見たところである。前面からみた構成は、PM(Power Module)を左右に各 2 スロット、MCH(MTCA Carrier Hub)を左右に各 1 スロット設けており左右で冗長システムになっている。CU(Cooling Unit)は下側に前面吸い込み、上側に背面掃出しの各 1 台実装している。AMC スロットは、左側 4 スロットが Single-width Full size に対応して CPU カードや HDD カードなど既存の AMC を使うことができる。右側 4 スロットは、 $\mu$  RTM にも対応している Double-width Full size のスロットとなっている。

新しい制御ボードと Power Bridge 社製の PM および NAT 社製の MCH による相互接続が正常にできることを確認した。現在、サンリツオートメイション社製の MCH を使った相互接続性確認を行っている。

Figure 3: MTCA.4 Shelf (front view)

Figure 4: MTCA.4 Shelf (rear view)

## 3.3 ドータカードの FMC への変更

I/O や機能拡張用のドータカードを独自の形状から ANSI/VITA57.1 の FMC に変更した。既存の様々な拡張機能を持つ FMC と組み合わせることができる。例えば、ビーム診断用のカメラで使われている Camera Link は既成品の FMC を使うことができる。これにより、新規にドータカードを開発することなく、システムの開発が可能となる。また、「Zynq」の PL 部でリアルタイム処理、PS 部でソフトを活かした複雑な処理を行うことで、FPGA ボードと CPUボードによる複数のボード構成を一枚のボードに集約できる可能性がある。そのため、画像など大容量のデータ伝送による時間的ロス、システムリソースの無駄使いなどが解消できると考えられる。

#### 3.4 FPGA「Zynq」の搭載

FPGA による処理性能を向上させるため、Xilinx 社製 28nm プロセス SOC (System on Chip) FPGA 「Zynq」を採用した。Zynq は、プロセッサとして ARM Coatex-A9 が内蔵され、ロジック回路部分は最新の Kintex 7 と同じ性能であり、プロセッサとロジックブロックがワンチップになっている。現行の Virtex5FXT とは異なり、CPU とその周辺回路の独立性が向上しており、ロジックブロックの論理回路の配置配線が CPU の動作性能に影響を与えにくくなっている。起動プロセスも変更があり、PS 部が起動した後に PL 部をコンフィグレーションしている。

Table 1 に現行の制御ボードに使っていた Virtex5 FXT と新しい制御ボードに使っている Zynq の性能比較を示した[10][11]。ロジックブロック部分では、Logic Cell が約 5 倍、Flip Flop が約 10 倍、内部 RAM が約 2.5 倍、DSP ブロックが約 6 倍になっている。プロセッサ部分では、CPU が PPC440 から Dual-Core Cortex-A9 に代わり FPU も拡張されており、内部 CPU バスが PLB (Processor Local Bus) から AMBA AXI-4 (Advanced Microcontroller Bus Architecture Advanced eXtensible Interface 4) に向上されている。

Table 1: Virtex5FXT vs Zynq

|                      | Virtex5 FXT XC5VFX70T-1FFG1136C       | Zynq XC7Z045-1FFG900C                        |

|----------------------|---------------------------------------|----------------------------------------------|

| Logic Cell           | 71,680                                | 350,000                                      |

| Flip Flop            | 44,800                                | 437,200                                      |

| RAM                  | 820kB                                 | 2,180kB                                      |

| DSP                  | 148                                   | 900                                          |

| PCIe                 | Gen1×8                                | Gen2×4                                       |

| Processor            | IBM PowerPC 440                       | Dual-ARM Cortex-A9 MP Core with CoreSight    |

| Processor Extensions | _                                     | NEON, Single and double precision vector FPU |

| CPU Freq.            | Up to 550MHz                          | Up to 667MHz                                 |

| L1 cashes            | 32kB Instruction / Data per processor | 32kB Instruction / Data per processor        |

| L2 cashes            | _                                     | 512kB                                        |

| On-Chip Memory       | _                                     | 256kB                                        |

| Internal Connect     | PLB                                   | ARM AMBA AXI-4                               |

#### 3.5 新しい制御ボードのハードウェア構成

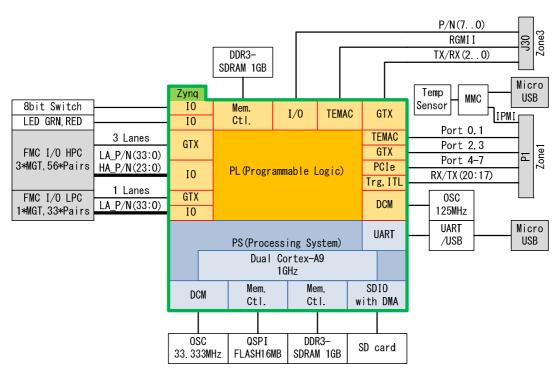

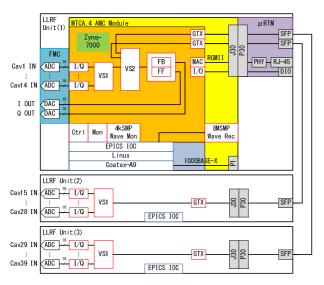

Figure 5 に機能ブロック図を Table 2 にボードのハードウェア構成を示した。

Zonel の AMC コネクタの Port  $1 \sim 7$  には、Zynq の高速シリアル IO を接続しており、Port0,1 には Ethernet、Port4 $\sim 7$  には PCIe $\times 4$  を接続した。MTCA.4 で新たに追加されたタイミング信号バスのRX/TX[20..17]も接続した。

MTCA.4 で追加された Zone3 の接続は、J30 のみ 実装した。今回は、 $\mu$  RTM に実装した Ethernet PHY チップとのインタフェイスの RGMII と 2 系統の SFP に接続されている高速シリアル信号および、その他 の 8 ビットの差動信号を接続した。Ethernet は、こ この RGMII もしくは、AMC コネクタ(Zone1)の どちらかを使えるようになる。

Zynq の PL 部に接続した機能拡張用の FMC スロットを HPC および LPC の 2 系統設けた。HPC 側はユーザー定義で利用できる差動信号 LA[33..0]および HA[23..0]をサポートした。さらに、マルチギガビットインタフェイスを送受信ペアで 1lane といい、3lanes の高速シリアルポートを接続した。もう一方の LPC 側は LA[33..0]と 1lane の高速シリアルポートを接続した。

FMC に実装した A/D や D/A と新しい制御ボード上の FPGA 間を低レイテンシで多ビットのデータをやり取りする時は、パラレルポートの LA およびHA を使う。逆に、レイテンシが影響のないデータについては、高速シリアルポートにてデータの入出力をする。

#### **PASJ2014-SUP103**

DDR3-SDRAM は1GB を2系統、PL 部およびPS 部に接続した。PL 部に接続した SDRAM は、A/D から入力されるサンプリングデータをリアルタイムに記録しており、異常イベントが発生した時に停止させ、記録データを読み出し異常発生の原因分析に使うことができる。PS 部に接続した SDRAM は、CPU のワーク用メモリとして使う。

FPGA の起動用デバイスには、16MB の QSPI Flash-ROM もしくは、SD card を準備した。基本的には SD card に保存した FPGA コンフィグレーションンファイル(bit ファイル)およびブートローダ(uboot)と Linux カーネルによって起動する[12]。 Linux が起動している時、FPGA コンフィグレーションファイル等をリモートでアップデートすることができる。遠隔 PC より、起動中の Linux に Telnet でリ

モートログインして、マウントされている SD card のファイルを書き換えリブートすると、更新した回路で起動することができる。

IPMI v1.5 に準拠したコントローラが実装されており、MCH と通信することで、電源の ON/OFF およびボード上の電圧および温度をモニタすることができる。また、フロントパネルのレバーの抜き差しでホットスワップを実現した。

その他に、8bit の DIP-Switch があり、例えば同一機能のボードが複数枚ネットワークに接続されているとき、EPICS レコード名の共通部分とは別に、DIP-SW の設定に応じた接頭語を追加して、識別に利用する。フロントパネルの 3 種類の LED は、ボードの動作状態を示す。青色はホットスワップ、赤色はエラー状態、緑色は動作状態を示している。

Table 2: Specifications of new control board

| FPGA                  | Zynq XC7Z045-1FFG900C                                              |

|-----------------------|--------------------------------------------------------------------|

| OS                    | Linux (EPICS-IOC)                                                  |

| RAM                   | DDR3-SDRAM 1GB×2 (PL, PS)                                          |

| FPGA Configuration    | QSPI FLASH-ROM 16MB, SD card, Remote Update                        |

| FMC slot              | High pin Count $\times 1$ , Low pin Count $\times 1$               |

| Zone1 (AMC Connector) | Port[0:1]:1000BASE-BX, Port[2:3]: Reserved (GTX), Port[4:7]: PCIe  |

|                       | Port[17:20]:M-LVDS, IPMB: IPMI v1.5 support                        |

| Zone3 (ZD connector)  | RGMII, GTX $\times$ 3, I/O $\times$ 8pairs                         |

| Switch                | 8bit DIP-switch                                                    |

| Front Panel LED       | Hot swap status (blue), Error status (red), Running status (green) |

| Size                  | PCIMG MTCA.4 Double-Width Full Size 148.5*28.95*181.5 [mm]         |

Figure 5: Block Diagram of new control board

#### 4. STF2 の LLRF

ILC(国際リニアコライダー)の実現に向けて STF(超伝導 RF 試験施設)では開発・試験を行っている。この ILC の高周波源は、1 台のマルチビームクライストロンで 39 台の超伝導空洞へ供給する 構成となる。そのため、39 空洞の空洞波形の振幅・位相をベクタサムして合成し、ディジタル信号処理でフィードバック・フィードフォワード制御を行なう。 STF では ILC 準拠の超伝導空洞を 12 台用いてビーム加速を行う STF2 加速器を計画している。

新しい制御ボードを STF2 加速器のディジタル LLRF システムに適用する。ここでは、AD×14ch、 D/A を 2ch 実装したダブル幅の FMC を新たに開発 し、新しい制御ボードと組み合わせてディジタル LLRF 制御ボードとしている。

ディジタル LLRF 制御ボードは、14ch の ADC 入力のため、39 空洞分のピックアップ信号には3台必要となる。39 空洞を並べると全長で 60m 程度と離れているため、3 台のディジタル LLRF 制御ボードを分散して配置する必要がある。1 台あたりのコストを抑えるために、MTCA.4 のシェルフを使わずに、1 台のディジタル LLRF 制御ボードが収納できる専用の 19 インチラックサイズの電源供給ボックスとし、LLRF Unit とした。

分散して設定された3台のLLRF Unitにより、それぞれで空洞からのピックアップ信号をA/D変換しそれぞれベクタサムを行い、マスタとなるユニットへSFP経由で光通信にて集約する。そこで、最終的なベクタサムをおこないフィードバック制御をし、D/A変換しベースバンドで出力しモジューレータ経由クライストロンそして空洞へ入力する。

今後、ソフトウェアを改善し機能性能確認を進めていく予定である。

Figure 6: Block Diagram of LLRF for STF2

## 5. まとめ

最新の SoC FPGA である「Zynq」を搭載した MTCA.4 規格に準拠した新しい制御ボードを開発した。 2 つの FMC スロットおよび  $\mu$  RTM を使った機能拡張が可能となり、様々なアプリケーションに適用することできる。また、Zynq 内部の最新 FPGA「kintex7」と同等性能のロジック回路により高度で高速なリアルタイム演算処理と、ARM Cortex-A9 にLinux を組込むことで EPICS を含む多様なソフトウェアも組み込むことができる。そして、FPGA 内でハードウェアとソフトウェアを連携させよりユーザビリティの向上を図ることができる。

今後、STF2 LLRF をはじめ加速器制御の高度化の ためにこの新しい制御ボードが使われる予定である。

## 参考文献

- [1] M. Ryoshi et al., "LLRF Board in Micro-TCA Platform", Proceedings of the 7th Annual Meeting of Particle Accelerator Society of Japan, Himeji, Aug., 2010.

- [2] T. Miura, et al., "Digital feedback system using μTCA for DRFS", Proceedings of the 8th Annual Meeting of Particle Accelerator Society of Japan (2011)

- [3] M. Omet, et al., "Development and Application of a Frequency Scan-based and a Beam-based Calibration Method for the LLRF Systems at KEK STF", Proceedings of the 9th Annual Meeting of Particle Accelerator Society of Japan (2012)

- [4] T. Kobayashi, et al., "Prototype Performance of Digital LLRF Control System for SuperKEKB", Proceedings of the 8th Annual Meeting of Particle Accelerator Society of Japan (2011)

- [5] S. Michizono, et al., "Tuner control for cERL cavities by digital feedback system", Proceedings of the 9th Annual Meeting of Particle Accelerator Society of Japan (2012)

- [6] H. Ishii, et al., "Development of a beam position detector for an orbit feedback system in SuperKEKB", Proceedings of the 8th Annual Meeting of Particle Accelerator Society of Japan (2011)

- [7] T. Kobayashi, et al., "RF Reference Distribution System for SuperKEKB", Proceedings of the 10th Annual Meeting of Particle Accelerator Society of Japan (2013)

- [8] K. Hayashi, et al., "Refinements of the new LLRF Control System for SuperKEKB", Proceedings of the 9th Annual Meeting of Particle Accelerator Society of Japan (2012)

- [9] http://mtca.desy.de/

- [10] Virtex-5 Family Overview DS100(v5.0) Feb.6,2009 ds100.pdf

- [11] Zynq-7000 All Programmable SoC Overview DS190(v1.6) Dec.2,2013 ds190-Zynq-7000-Overview.pdf

- [12] H. Deguchi et al., "Linux and EPICS embedding on MTCA.4 FPGA(ZYNQ) board", in this meeting.