# KEK における SLAC P2 Marx 型クライストロン電源のテストスタンド TEST STAND FOR THE SLAC P2 MARX KLYSTRON MODULATOR AT KEK

中島啓光<sup>#)</sup>, 明本光生, 設楽哲夫, 本間博幸, 松本利広, 福田茂樹, 道園真一郎 Hiromitsu Nakajima <sup>#)</sup>, Mitsuo Akemoto, Tetsuo Shidara, Hiroyuki Honma, Toshihiro Matsumoto, Shigeki Fukuda, Shinichiro Michizono

High Energy Accelerator Research Organization

#### Abstract

A unit of the P2 Marx, which has been developed and already tested as a pulse power supply for a 10MW multi-beam klystron for the International Linear Collider at SLAC National Accelerator Laboratory, is being manufactured for evaluation purpose at KEK. The P2 Marx consists of 32 cells, each of which has control system "hardware manager" and four gate drivers, which have hardware for fast detection and response to faults. It is essential that each of the cells and the gate drivers be tested before doing the test of the whole the P2 Marx. This paper describes the 2 cells test stand and the gate driver tester at KEK.

# 1. はじめに

国際リニアコライダー (ILC) では、RF 源として 10MW マルチビームクライストロンが使用される予 定となっている。高エネルギー加速器研究機構 (KEK) では、これまで 10MW マルチビームクラ イストロン用の電源として、パルストランスを使用 したバウンサー回路付きの電源の開発を行ってきた [1]。しかし、要求されるパルス幅が 1.65ms と長く、 パルストランスとそのオイルタンクが大きくなって しまうことなどから、ILC の Technical Design Report (TDR) では、10MW マルチビームクライストロン 用の電源として、パルストランスを使用しない半導 体スイッチを使用した Marx 型の電源がベースライ ンデザインに採用された[2]。KEK では、昨年度から 長岡技術科学大学との共同研究で ILC 用の Marx 型 クライストロン電源の開発を行っている[3]。一方、 SLAC National Accelerator Laboratory (SLAC) では、 ILC 用のクライストロン電源として、半導体スイッ チを使用した Marx 型の電源の開発が 10 年以上前か ら進められており、すでに第二世代となる P2 Marx が開発され、試験運転が行われている[4,5]。KEK で は、今年度、長岡技術科学大学との共同研究と平行 して、P2 Marx 型のクライストロン電源をその評価 のために製作することとなった[6]。

## 2. P2 Marx

## 2.1 半導体スイッチを使用した Marx 電源

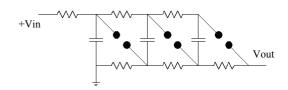

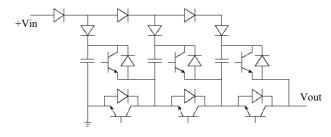

Marx 型の電源は、Figure 1 (a) に示すように、充電抵抗を介して、複数のコンデンサを並列に充電し、ギャップスイッチによってそれらを直列に放電することで、コンデンサの充電電圧の段数倍のインパルス電圧が得られるものである。半導体スイッチを使用した Marx 型の電源では、Figure 1 (b) のように充電と放電のスイッチに半導体スイッチを使用し、

各段の ON/OFF のタイミングをコントロールすることにより、出力パルス電圧波形の調整が可能となる。Marx 型の電源は、低い充電電圧でも段数を増やすことによって、高電圧を得ることができ、各段のスイッチにかかる電圧は、充電電圧と同じであるため、低電圧の半導体スイッチが使用できる。ILC 用の電源としては、Marx 回路の各段の充電電圧、出力パルス電圧の補正の方式等により、いくつかのタイプが研究、開発されている。

(a) Classic Marx topology (3 cell).

(b) Solid-state Marx topology (3 cell).

Figure 1: Simplified of the Marx topology.

#### 2.2 P2 Marx の概要

ILC におけるクライストロン用電源に要求される主な仕様を Table 1 に示す。ILC の主ライナックでは、378 台のクライストロン用電源が使用されるため、コスト、信頼性、メンテナンス性、サイズ、効率なども重要となる。P2 Marx は、これらを考慮して SLAC で設計、開発されたものであり、すでに試験運転が行われ、その性能が確認されている。

<sup>#</sup> hiromitsu.nakajima@kek.jp

Table 1: ILC Klystron Modulator Parameters

| Output Voltage             | -120kV  |

|----------------------------|---------|

| Output Current             | 140A    |

| Pulse Width (flat-top)     | 1.65ms  |

| Pulse Repetition Frequency | 5Hz     |

| Output Pulse Flat-top      | < ±0.5% |

P2 Marx は、32 cell で構成されており、各 cell を-3.75kV に充電することで、-120kV のパルス電圧を出力する。各 cell の最大充電電圧は、-4kV であり、2 cell が故障しても-120kV のパルス出力が可能となっている。また、各 cell のサイズと重量は、メンテナンス性を考慮したものとなっており、筐体の前面から容易に交換可能な物となっている。P2 Marxの cell のパラメーターを Table 2 に示す。

Table 2: P2 Marx Cell Parameters

| Cell Weight          | <50lb            |

|----------------------|------------------|

| Cell Dimensions      | 13.75"×29.5" ×8" |

| Number of Cells      | 32               |

| Output Voltage (Max) | -4kV             |

| Average Cell Power   | 4.48kW           |

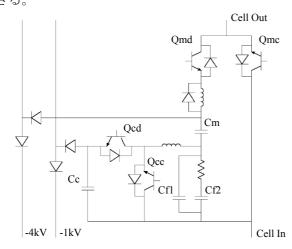

#### 2.3 P2 Marx の cell の動作

P2 Marx の各 cell は、メインパルス回路とそこに 直列に接続されたパルス補正回路によって構成され、 1.7ms のフラットなパルス電圧が出力できる。P2 Marx の cell の回路図を Figure 2 に示す。 Figure 2 に おいて、Qmc がメインパルス回路の充電用の IGBT、 Qmd が放電用の IGBT、Cm がメインパルス回路の コンデンサであり、出力のパルス電圧は、Cm の充 電電圧で決まる。パルス補正回路は、メインパルス 回路の放電中には、Cc を入力コンデンサ、Qcd をス イッチ、Cfl、Cf2 を出力コンデンサとした 0~-700V 出力のバックコンバータ回路として動作する。 パルス補正回路の出力電圧は、PC 上で計算された パターンによる PWM 制御によって調整される。ま た、各 cell の PWM の位相をずらすことで、32 cell 全体での出力パルス電圧のリップルを抑えることが できる。

Figure 2: Simplified cell schematic of the P2 Marx.

#### 2.4 P2 Marx の制御系

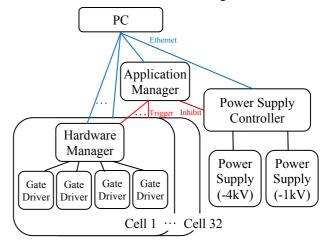

P2 Marx の制御系は、各 cell の制御を行う hardware manager、P2 Marx 全体の制御を行う application manager、充電電源のコントローラ、ユーザーインターフェースとなる PC で構成されている。P2 Marx の制御系のブロック図を Figure 3 に示す。

Figure 3: Block diagram of the P2 Marx control system.

各 cell の制御は、FPGA を使用した hardware manager によって行われ、ゲートドライバーへのトリガーの供給、各モニター値のデジタル化、リレーの制御等を行っている。また、IGBT の過電流等のインターロックは、各 cell に 4 つあるゲートドライバーでそれぞれハード的に行われている。hardware manager は、光ファイバによって絶縁され、グランドレベルの Gigabit Ethernet スイッチに接続されている。

P2 Marx 全体の制御は、application manager によって行われており、モジュレータ全体に関わるインターロック、各 cell に供給しているトリガー信号の制御、充電電源へのインヒビット信号の制御を行っている。また、-4kV と-1kV の充電電源の制御、モニターは、充電電源コントローラによって行われ、application manager と充電電源コントローラは、共に Ethernet に接続されている。

ユーザーインターフェースとなる PC は、Ethernet を介して、hardware manager、application manager、充電電源のコントローラと通信を行い、各種のステータスやモニター値の表示、ON/OFF の制御、充電電圧の設定等を行う。また、PWM のパターンは、PC 上で出力のパルス電圧がフラットになるように計算され、各 cell の hardware manager に送信される。

# 3. 試験装置

# 3.1 試験装置の概要

P2 Marx は、32 cell で構成されるが、各 cell は hardware manager によって独立に制御されており、動作試験は、cell ごとに行うことができる。また、各 cell には、4 つのゲートドライバーがあり、それぞれ独立にインターロックの回路を持っている。各

cell 及び、ゲートドライバーの動作は、IGBT 及び負荷であるクライストロンの保護に関わる重要なものであり、その動作試験が必要不可欠となる。

## 3.2 ゲートドライバーのテスター

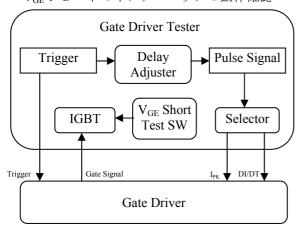

ゲートドライバーは、hardware manager からトリガー信号をもらい、IGBT を駆動するゲート信号を出力する。各 cell には、メインパルス回路の充電用と放電用、パルス補正回路の充電用と放電用と放電用で 4 つのゲートドライバーがある。ゲートドライバーのテスターは、ゲートドライバーにトリガー及び過電流の信号を入力し、ゲート電圧波形の確認、各インターロックの動作確認を行うためのものである。ゲートドライバーのテスターのブロック図を Figure 4 に示す。また、主な確認項目を下記に示す。

- V<sub>GE</sub>のパルス電圧の確認

- V<sub>CE</sub>のパルス電圧の確認

- I<sub>PK</sub> インターロックの動作確認

- DI/DT インターロックの動作確認

- $V_{GE}$ ショートのインターロックの動作確認

Figure 4: Block diagram of the gate driver tester.

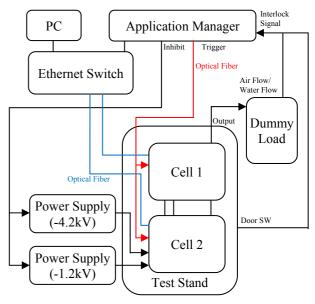

# 3.2 テストスタンド

KEK では、2 cell の試験を行うためのテストスタンドを製作する予定であり、現在、詳細に関する検討を行っている。テストスタンドは、application manager、PC、充電電源(-4.2kV、-1.2kV)、模擬負荷、及び 2 cell を収容するケースで構成される。テストスタンドのブロック図を Figure 5 に示す。

テストスタンドでは、2 cell を収容するケースの 扉のインターロック等を受けて、各 cell へのトリ ガー信号、充電電源へのインヒビット信号の制御を 行うために、application manager が必要となる。ま た、application manager を Ethernet に接続すること によって、PC から充電の ON/OFF、トリガーの ON/OFF を行えるようにする。

テストスタンドで必要となる充電電源は、2 cellでフルスペックの運転をした場合、メインパルス回路用で約 10kW、パルス補正回路用で約 2kW の容量が必要となる。また、それぞれの充電電源は、application manager からのインヒビット信号を受けて、充電を停止する必要がある。P2 Marx では、PC

からメインパルス回路の充電電圧を設定しているが、 テストスタンドではローカルで行う。

模擬負荷は、8kV、140A、1.7ms、5pps の運転を行うと、約 $60\Omega$ で約10kW の抵抗が必要となる。抵抗は、空冷式あるいは、水冷式を検討しており、それぞれファンまたは、冷却水のインターロックをapplication manager に入力する予定である。また、負荷短絡試験のために、模擬負荷に並列にギャップスイッチ等を入れることを検討している。

Figure 5: Block diagram of the 2 cell test stand.

# 4. まとめと今後の予定

KEKでは、P2 Marx型のクライストロン電源の制作のために必要となるゲートドライバーのテスター、2 cell のテストスタンドの設計、製作を進めている。ゲートドライバーのテスターは、部品がほぼ揃い、現在、製作中となっている。2 cell のテストスタンドに関しては、現在、詳細に関する検討を行っており、年内の完成を目標としている。

#### 参考文献

- [1] M. Akemoto, et al., "KEK 超伝導加速器試験施設(STF)に於ける 10MW クライストロン用長パルスモジュレータの開発", Proceedings of Particle Accelerator Society Meeting, pp.773-775, 2009.

- [2] ILC Technical Design Report Volume 3 Accelerator, 2013, http://www.linearcollider.org/ILC/Publications/Technical-Design-Report.

- [3] Y. Kozasa, et al., "ILC 用半導体マルクス電源", these proceedings, SAP055.

- [4] M.A. Kemp, et al., "Final Design of the SLAC P2 Marx Klystron Modulator", Proceedings of Pulse Power Conference, Chicago, IL, USA, 2011.

[5] M.A. Kemp, et al., "The SLAC P2 Marx", Pulse Power

- [5] M.A. Kemp, et al., "The SLAC P2 Marx", Pulse Power Proceedings of International Power Modulator and High Voltage Conference, San Diego, CA, USA, 2012.

- [6] M. Akemoto, et al., "KEK における ILC クライストロン電源開発の現状", these proceedings, MOOL07.